Trong hướng dẫn này, chúng ta sẽ tìm hiểu về cơ chế đồng hồ trong LPC2148. Ở đây chúng ta sẽ thảo luận mọi chi tiết về cấu hình của Clock và PLL trong LPC2148 ARM7 Microcontroller. Có một số cách chúng ta có thể đồng hồ ARM vi điều khiển. Một cách là sử dụng Đồng hồ bên ngoài với chu kỳ nhiệm vụ 50-50 và trong dải tần số từ 1 MHz đến 50 MHz được kết nối với Pin XTAL1. Cách thứ hai là bằng cách kết nối External Oscillator bên ngoài nhưng phạm vi của nó là thấp hơn giữa 1 MHz đến 30 MHz . Chúng tôi cũng có thể sử dụng chip PLL Oscillator nhưng ở đây tần số xung nhịp bên ngoài không được vượt quá phạm vi từ 10 MHz đến 25 MHz . Trong hướng dẫn này, chúng ta sẽ tập trung vào tinh thể bên ngoài với PLL. Nguồn đồng hồ bên ngoài và tinh thể bên ngoài chỉ sẽ được thảo luận trong tương lai vì nó không được yêu cầu tại thời điểm này.

Cơ chế: PLL trong LPC2148 ARM7

PLL (Phase Lock Loop) là gì?

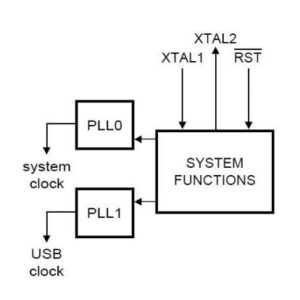

PLL được sử dụng để tạo ra đồng hồ hệ thống từ 10 MHz đến 25 Mhz. PLL có thể nhân tần số từ 10 MHz đến 60 MHz (LPC21xx Series) và 48 MHz cho USB nếu được sử dụng. PLL sử dụng hệ số nhân tần số có thể nằm trong khoảng từ 1 đến 32, trong tình huống thực tế, giá trị này không được cao hơn 6 do giới hạn tần số trên. Máy phát PLL cho phép chạy ARM ở tốc độ cao với bộ dao động tần số thấp được kết nối. Ngoài ra, điều này giảm thiểu phát thải EMC khi tần số được nhân lên bên trong chip ARM. PLL cho phép thay đổi tần số động. Trong LPC2148 vi điều khiển có hai PLLs cung cấp tần số lập trình cho CPU và hệ thống USB. [ PLL0: Dành cho Đồng hồ Hệ thống , PLL1: Dành cho Đồng hồ USB ]

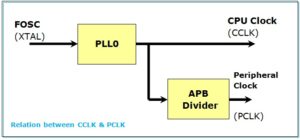

Bộ vi xử lý ARM7 LPC2148 cần hai đồng hồ; một là dành cho các thiết bị ngoại vi của nó và một cho CPU của nó. CPU hoạt động nhanh hơn với tần số cao hơn trong khi nhu cầu ngoại vi tần số thấp hơn để làm việc. Đồng hồ ngoại vi (PCLK) và Đồng hồ CPU (CCLK) lấy đầu vào đồng hồ từ một PLL hoặc từ nguồn bên ngoài. Sau khi RESET, cấu hình của PLL (Phase Lock Loop) và VPB (VLSI Peripheral Bus) Divider sẽ là điều đầu tiên cần làm.

Bản thân PLL sử dụng CCO (Bộ điều khiển hiện tại được điều khiển) hoạt động trong phạm vi từ 156 MHz đến 320 MHz, do đó có bộ chia bổ sung giữ CCO trong phạm vi của nó, trong khi PLL cung cấp tần số mong muốn. Đồng hồ đầu ra được tạo ra bằng cách chia tần số CCO bằng 2, 4, 8, 16. Bộ chia tối thiểu là '2' vì vậy đầu ra của PLL sẽ luôn có chu kỳ nhiệm vụ 50% cho chắc chắn.

Đồng hồ ngoại vi tức là PCLK có nguồn gốc từ CPU Clock tức là CCLK. Bộ chia APB quyết định tần số hoạt động của PCLK. Đầu vào cho Bộ chia APB là CCLK và đầu ra là PCLK. Theo PCLK mặc định chạy ở tốc độ 1/4 tốc độ của CCLK. Để điều khiển APB Divider, chúng ta có một thanh ghi có tên VPBDIV. Giá trị trong VPBDIV kiểm soát việc chia CCLK để tạo PCLK như sau:

| VPBDIV =0x00 | Đồng hồ bus APB (PCLK) là một phần tư của đồng hồ bộ xử lý (CCLK) |

| VPBDIV =0x01 | Đồng hồ bus APB (PCLK) giống với đồng hồ bộ xử lý (CCLK) |

| VPBDIV =0x02 | Đồng hồ bus APB (PCLK) là một nửa bộ xử lý (CCLK) |

| VPBDIV =0x03 | Kín đáo. Nếu giá trị này được ghi vào thanh ghi APBDIV, nó không có hiệu lực (cài đặt trước đó được giữ lại). |

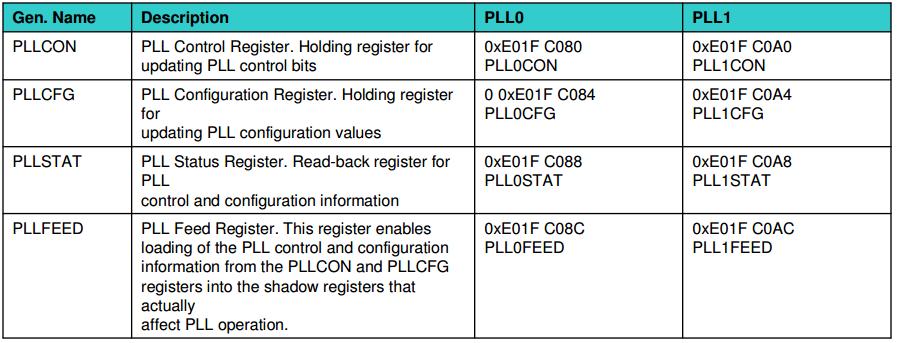

Đăng ký PLL trong LPC2148

Đăng ký PLL được liệt kê ở đây, để biết thêm chi tiết, hãy làm theo bảng dữ liệu:

PROGRAMMING: PLL trong LPC2148 ARM7

Trong khi cấu hình đồng hồ và PLL trong LPC2148 ARM7. Chúng ta phải làm theo các bước chung. Điều quan trọng là phải làm theo trình tự để thực hiện một phần cấu hình của PLL

- Chọn tần số hoạt động mong muốn cho hệ thống của bạn (Tần số hoạt động CPU) CCLK

- Kiểm tra bộ dao động được kết nối với bộ điều khiển trên bo mạch FOSC

- Tính toán giá trị của PLL Multiplier 'M' CCLK = M x FOSC

- Tìm giá trị của PLL Divider 'P' theo cách từ 156 MHz đến 320 MHz, 156 <FCCO <320 = CCLK x 2 x P

- Viết giá trị PLLCON và PLLCFG

- Viết PLLFEED giá trị 0xAA và 0x55

- Chờ PLL khóa

- Kết nối PLL

- Viết PLLFEED giá trị 0xAA và 0x55 một lần nữa

VÍ DỤ: Đặt PLL trong LPC2148

Chúng tôi có 12 MHz tinh thể kết nối với LPC2148 trên bo mạch phát triển vi điều khiển của chúng tôi. Chúng ta có thể nói FOSC = 12 MHz. Và chúng tôi muốn lõi được chạy ở tần số 60 MHz. Trong trường hợp này, chúng ta phải nhân tần số tinh thể ie12 MHz bằng '5'

| CCLK = M x FOSC = 5 x 12 = 60 MHz |

Ngoài ra chúng ta phải giữ FCCO (tần số của bộ điều khiển dao động hiện tại PLL) trong phạm vi của nó tức là [156 MHz - 320 MHz], vì vậy chúng ta phải kiểm soát một hằng số 'P' khác:

| FCCO = CCLK x 2 x P |

| FCCO = 60 MHz x 2 x 2 = 240 MHz |

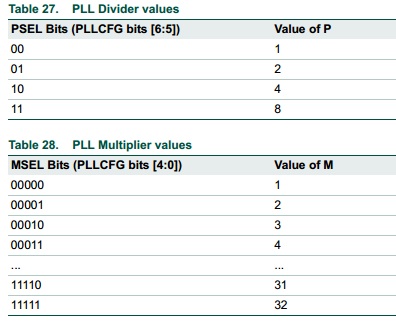

Vì vậy, chúng tôi thấy P = 2 đáp ứng các yêu cầu của FCCO (Lập trình 156 MHz PLL phải được thực hiện trong một số trình tự để làm cho thiết lập PLL mới có hiệu quả. Trước tiên, chúng ta phải ghi các giá trị M và P chia cho PLLCFG Register. có thể rất cụ thể, như thể hiện trong bảng dưới đây

GHI CHÚ: Đối với thanh ghi PLLCFG, chúng ta phải sử dụng giá trị (M-1) cho các bit MSEL trong đó M là giá trị thu được từ các phương trình. Ví dụ, nếu chúng ta muốn sử dụng M = 5 từ phương trình thì chúng ta phải áp dụng một giá trị (M-1) = (5-1) = 4 cho thanh ghi. Tương tự, chúng ta phải sử dụng một giá trị cụ thể cho các bit PSEL như đã đề cập trong bảng trước đó. Do đó với P = 2, chúng ta phải gán 01 cho PSEL. Đọc kỹ bảng

Vì vậy, để tính M = 5 và P = 2 , thì PLLCFG = 0b00100100 = 0x24;

Hơn nữa, phải theo một số trình tự để kích hoạt PLL. Sau khi đăng ký PLLCFG được cập nhật sau đó cập nhật đăng ký PLLCON và sau đó chúng tôi phải viết 0xAA và sau đó đăng ký 0x55 đến PLLFEED . Giá trị này phải được viết trong các chu kỳ liên tiếp. Đây là một ví dụ.

Đây là cách bạn có thể cấu hình Clock và PLL trong LPC2148 ARM7 Microcontroller. Trong hướng dẫn tiếp theo, chúng ta sẽ khám phá tính năng hẹn giờ trong LPC2148 ARM7 , nơi chúng ta sẽ khám phá việc sử dụng PLL với một dự án ví dụ.

Không có nhận xét nào:

Đăng nhận xét